# Jetson Nano Developer Kit 40-Pin Expansion Header GPIO Usage Considerations

**Application Note**

# **Document History**

#### DA-09753-001\_v1.0

| Version | Date              | Description of Change |

|---------|-------------------|-----------------------|

| 1.0     | February 13, 2020 | Initial Release       |

## Table of Contents

| Introduction1                             |

|-------------------------------------------|

| TXB0108 Level Shifter                     |

| TXB Voltage Translator Architecture       |

| "Keeper" Pull-up and Pull-down Resistors4 |

| Driving Capacitive Loads4                 |

| Output Enable5                            |

| Jetson Nano Developer Kit Examples        |

# List of Figures

| Figure 1. | TXB Devices Typical Usage                            | 2 |

|-----------|------------------------------------------------------|---|

| _         | TXB Device Usage on Developer Kit Carrier Board      |   |

| Figure 3. | Simplified TXB0108 Architecture Diagram              | 3 |

| Figure 4. | One TXB Connection from Jetson Nano to 40-Pin Header | 6 |

| Figure 5. | Audio Codec (12S and MCLK) Example Connections       | 7 |

| Figure 6. | Button and LED Example Connections                   | 7 |

## Introduction

This application note describes how to work with the signals on the 40-pin expansion header on the NVIDIA® Jetson Nano™ Developer Kit carrier board. All signals routed to this connector from the Jetson Nano module, except for the I2C interfaces, pass through TI TXB0108RGYR level shifters. This is necessary to level shift the signals from 1.8V levels from the module to 3.3V levels at the expansion connector pins. This level shifter retains the ability to pass bidirectional signals without the need for a direction pin. There are some considerations that must be considered when using the signals that come from (or go to) these level shifters. These considerations are described in this application note.

### TXB0108 Level Shifter

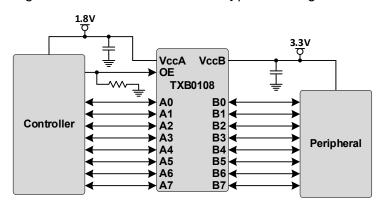

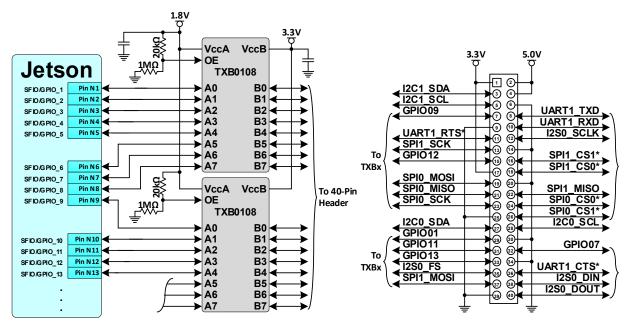

Figure 1 shows the usage of the TXB devices and Figure 2 shows the TXB on the carrier board.

Figure 1. TXB Devices Typical Usage

Figure 2. TXB Device Usage on Developer Kit Carrier Board

# TXB Voltage Translator Architecture

The TXB push-pull buffered architecture supports bidirectional signaling without the need for a direction control signal to select whether a pin is an output or an input. This type of device is intended to interface with push-pull CMOS output drivers or high impedance loads, such as standard CMOS inputs. The TXB0108 devices are not intended for use in open-drain applications or to drive low impedance (i.e. directly driving an LED) or high capacitive loads (i.e. driving a long wire, or multiple loads). To support driving either of these load types, an additional buffer/transistor/FET may be required.

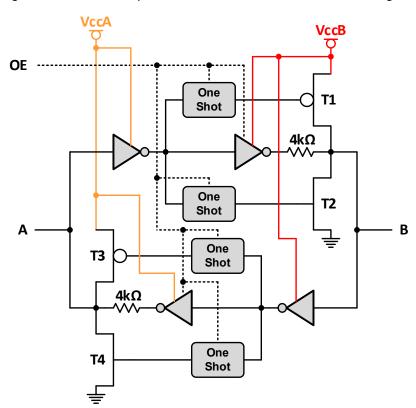

Figure 3. Simplified TXB0108 Architecture Diagram

The TXB level shifters have output buffers with  $\sim 4k\Omega$  resistors in series which make them very weak. A one-shot (OS) circuit is included to help with signal rise/fall times. The OS circuitry is enabled when a rising or falling edge is sensed at one of the inputs.

When an A-port pin is connected to a push-pull driver output or a strong pull-up/down resistor (equivalent to a push-pull driver) and driven high, the weak buffer (w/series resistor) drives the B-port high along with the OS circuit which is enabled when the rising edge is sensed. The Bport is driven high by both the buffer and T1 until the OS circuit times out after which only the weak buffer continues to drive the output.

If, instead, the external push-pull driver drives the A-Port pin low, the B-port will be driven low along with the OS circuit which is enabled when the falling edge is sensed. The B-port is driven low by both the buffer and T2 until the OS circuit times out and only the weak buffer continues to drive the output. (See Figure 3).

The TXB-type level shifter is called "weak-buffered," because it is strong enough to hold the output port high or low during a DC state with a high impedance load, but weak enough that it can easily be over driven by a push/pull driver (or strong pull-up/down resistor). This allows the device to support inputs or outputs on both the A- and B-port sides.

An external push-pull driver or strong pull-up/down resistor must be able to supply more than ±2 mA of current to reliably overdrive the weak output buffer which is always active as long as the OE pin is active (high). If a pull-up/down resistor is used to force a TXB pin to a high/low state, similar to a push-pull driver, the resistor should be ~VccX/2 (~1.65kΩ or stonger if VccX is 3.3V, or  $\sim 0.9 \text{k}\Omega$  or stronger if VccX is 1.8V.

# "Keeper" Pull-up and Pull-down Resistors

If the design requires weak "keeper" pull-up and down resistors on any of the lines connected to the TXB devices, the resistors must be weak. When the TXB outputs are in a steady high and low state, the weak buffer with the  $4k\Omega$  series resistor is driving the line. If an external "keeper" pull-up and down resistor is added, a resistor divider network is formed with the  $4k\Omega$ series resistor. If the "keeper" resistor value is too small, the level driven by the TXB buffer may not meet a valid VOH (high) or VOL (low) level. This could lead to unreliable operation. The value of the external "keeper" resistor should be >  $50k\Omega$ . It is better not to have these "keeper" resistors whenever possible as they will have little effect when the TXB devices are powered. In the case of the Jetson Nano Developer Kit carrier board design, the TXB level shifters OE is active whenever the system is powered on. There are very weak  $(1m\Omega)$  pull-downs on the OE pins to keep them disabled as the power comes on, and stronger (20k $\Omega$ ) pull-ups to 1.8V to enable the TXB devices once power is enabled.

## **Driving Capacitive Loads**

The TXB level shifters can drive up to about 70pF. If the load is much larger, the OS circuitry, which is enabled when a rising and falling edge is detected, is enabled for ~5ns. If the capacitive load is too large, the OS will timeout before the signal reaches a fully high or low level. After that, the signal will continue to rise and fall, but only driven by the weak output buffer which can lead to slower than desired rise and fall times.

## Output Enable

The TXB level shifters have an output enable (OE) pin. When low, the outputs (weak buffers and OS circuits) are disabled. When high, the weak buffers are enabled always, and the OS circuits are enabled when a rising and falling edge is detected. The Jetson Nano Developer Kit carrier board pulls the OE pins to 1.8V, so they are always enabled when the system is powered on.

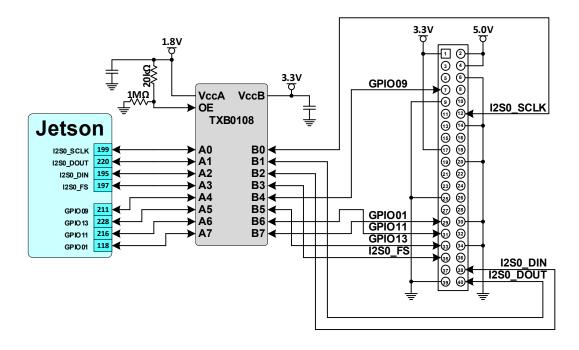

## Jetson Nano Developer Kit Examples

Following are several examples where pins from the 40-pin expansion header are connected to some device or circuit and some things to consider. The following figure shows eight signals from Jetson Nano that are routed to one of the TXB level shifters and then to the 40-pin expansion header. These signals support the following options on Jetson Nano:

- ▶ 12S0\_SCLK: Audio 12S interface shift clock or GPIO

- ▶ 12S0 DOUT: Audio 12S interface shift clock or GPIO

- ▶ 12S0 DIN: Audio 12S interface shift clock or GPIO

- ▶ 12S0 FS: Audio 12S interface shift clock or GPIO

- ► GPI009: GPI0 or Audio Master Clock

- ► GPI013: GPI0 or PWM

- ► GPI011: GPI0 or General Purpose Clock

- ► GPI001: GPI0 or General Purpose Clock

Figure 4. One TXB Connection from Jetson Nano to 40-Pin Header

The following example shows possible connection of the Jetson Nano I2SO interface and GPI009 (Audio MCLK) Audio Codec.

GPIO09 Audio Codec I2S0\_SCLK **►** SCLK **►** FS DIN **DOUT** MCLK GPIO01 GPIO11 GPIO13 ×12S0\_FS 36) **③** 12SO DIN 37

I2S0\_DOUT

⊛

<u>40</u>-**③**

Figure 5. Audio Codec (12S and MCLK) Example Connections

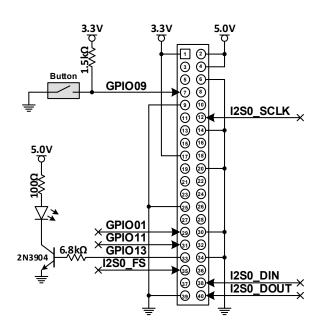

The following example shows possible connections to a button and an LED.

Figure 6. Button and LED Example Connections

#### Notice

This document is provided for information purposes only and shall not be regarded as a warranty of a certain functionality, condition, or quality of a product. NVIDIA Corporation ("NVIDIA") makes no representations or warranties, expressed or implied, as to the accuracy or completeness of the information contained in this document and assumes no responsibility for any errors contained herein. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This document is not a commitment to develop, release, or deliver any Material (defined below), code, or functionality.

NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and any other changes to this document, at any time without notice.

Customer should obtain the latest relevant information before placing orders and should verify that such information is current and complete. NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgement, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer ("Terms of Sale"). NVIDIA hereby expressly objects to applying any customer general terms and conditions with regards to the purchase of the NVIDIA product referenced in this document. No contractual obligations are formed either directly or indirectly by this document.

NVIDIA products are not designed, authorized, or warranted to be suitable for use in medical, military, aircraft, space, or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death, or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer's own risk.

NVIDIA makes no representation or warranty that products based on this document will be suitable for any specified use. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer's sole responsibility to evaluate and determine the applicability of any information contained in this document, ensure the product is suitable and fit for the application planned by customer, and perform the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer's product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this document. NVIDIA accepts no liability related to any default, damage, costs, or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this document or (ii) customer product designs.

No license, either expressed or implied, is granted under any NVIDIA patent right, copyright, or other NVIDIA intellectual property right under this document. Information published by NVIDIA regarding third-party products or services does not constitute a license from NVIDIA to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party, or a license from NVIDIA under the patents or other intellectual property rights of NVIDIA.

Reproduction of information in this document is permissible only if approved in advance by NVIDIA in writing, reproduced without alteration and in full compliance with all applicable export laws and regulations, and accompanied by all associated conditions, limitations, and notices.

THIS DOCUMENT AND ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE. TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL NVIDIA BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF NVIDIA HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Notwithstanding any damages that customer might incur for any reason whatsoever, NVIDIA's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms of Sale for the product.

#### ARM

ARM, AMBA and ARM Powered are registered trademarks of ARM Limited. Cortex, MPCore and Mali are trademarks of ARM Limited. All other brands or product names are the property of their respective holders. "ARM" is used to represent ARM Holdings plc; its operating company ARM Limited; and the regional subsidiaries ARM Inc.; ARM KK; ARM Korea Limited.; ARM Taiwan Limited; ARM France SAS; ARM Consulting (Shanghai) Co. Ltd.; ARM Germany GmbH; ARM Embedded Technologies Pvt. Ltd.; ARM Norway, AS and ARM Sweden AB.

#### Trademarks

NVIDIA, the NVIDIA logo, and Jetson Nano are trademarks and/or registered trademarks of NVIDIA Corporation in the U.S. and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.

#### Copyright

© 2020 NVIDIA Corporation. All rights reserved.